Flash Memory Overview on Toradex Products

Introduction

Flash memory is a non-volatile, electrically erasable and reprogrammable computer storage medium that is widely used in electronic devices. As all Toradex SoMs feature embedded flash memory, we are going to provide a brief overview of those.

If you are looking for overall information about eMMC memories with embedded Linux, partitioning and configurations, refer to eMMC (Linux).

If you are looking for content on flash health monitoring using Torizon, refer to our Blog: Flash Health Monitoring on Torizon.

Flash Memory Overview

Flash cells can be based on two main structures: NOR and NAND gates. The differing structures imply different characteristics, and certain advantages and disadvantages. The below table summarizes some of those.

| Advantages | Disadvantages | |

|---|---|---|

| NAND | Faster program-erase cycle Lower cost | Slow random access (read on pages) Harder byte programming Requires an error correction mechanism |

| NOR | Faster random access Easier byte programming Doesn’t require error correction | Slower program-erase cycle Higher cost |

NAND-based memories can be raw NAND or NAND memory integrated with a controller. This second approach is called eMMC, a solid-state storage standard derived from the MMC standard.

The webinar Flash Memory in Embedded Linux Systems, presented by Toradex, has a good introduction to the topic.

NAND Flash Technology

Toradex SoMs feature flash memories based on NAND technology.

In NAND Flash, the smallest unit of storage is the memory cell. In memory cells, data is encoded using different voltage levels. The different NAND types are capable of setting and reading a differing number of voltage levels, thus providing different data storage capacities per cell. The amount of bits stored per cell has increased as the technology has evolved.

NAND Flash Types

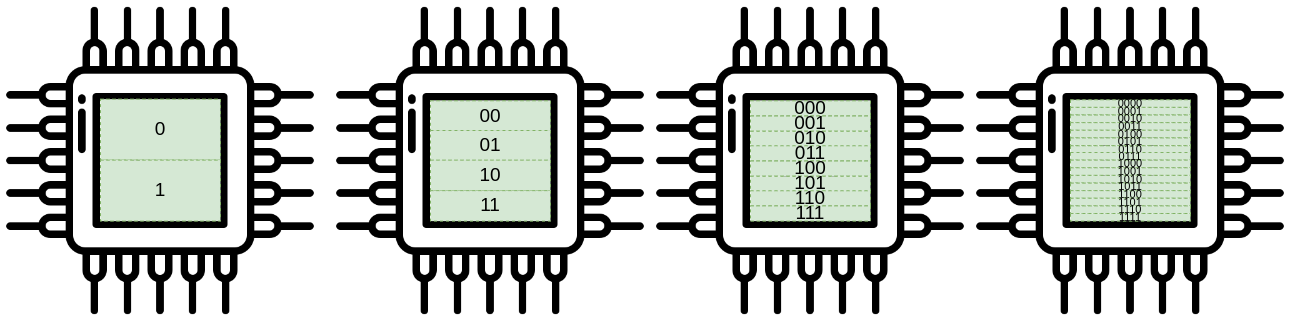

Considering the number of bits stored in each cell, NAND flashes can be classified as:

- Single-Level Cell (SLC): one data bit per cell (encoding values of 0b0 and 0b1 using two different voltage levels).

- Multiple-Level Cell (MLC): two data bits per cell (encoding values between 0b00 and 0b11 using four different voltage levels).

- Triple-Level Cell (TLC): three data bits per cell (encoding values between 0b000 and 0b111 using eight different voltage levels).

- Quadruple-Level Cell (QLC): four data bits per cell (encoding values between 0b0000 and 0b1111 using sixteen different voltage levels).

The diagram below provides a visual representation of the various NAND types:

NAND flash memories have a life span. The write and erase operations contribute to the wearing out of the cells and reduce their life span. An increasing number of worn-out cells can cause the flash memory to fail. The number of times each cell can be written and erased before it wears out is a significant property of these memories and is oftentimes referred to as endurance. The endurance is measured in program/erase cycles (P/E cycles). Different NAND types have differing endurances. In general, increasing the number of data bits stored per cell is contributing to the reduction of the endurance of the flash memory. As we see, the endurance of the NAND flash memory is directly related to the device's life span.

The table below shows a comparison of some of the important characteristics of the various NAND types.

| Cell Type | Endurance | Life span | Capacity per Cell | Cost per Capacity |

|---|---|---|---|---|

| SLC | Highest¹ | Highest¹ | 1 bit | High |

| MLC | High¹ | High¹ | 2 bit | Medium |

| TLC | High¹ | High¹ | 3 bit | Medium |

| QLC | Medium¹ | Medium¹ | 4 bit | Low |

¹: Assuming state-of-the-art memory devices

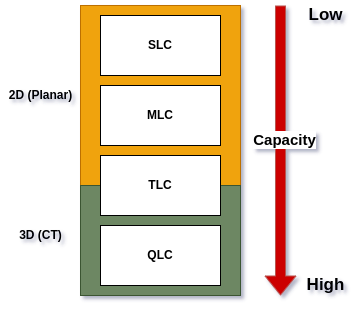

NAND Flash Arrangement

There are two main arrangements of NAND flash cells: 2D (planar) and 3D. The high demand for high-capacity and low-cost NAND flashes led to the development of the three-dimensional memory structure that provides for higher capacities than the 2D (planar) arrangements. The 3D arrangement has been enabled by the application of the so-called charge trap (CT) technology. Using the 3D arrangement, the capacity of the memory can be scaled up by applying multiple layers of cells atop each other. CT technology has simplified the implementation of TLC cells and has enabled the implementation of QLC cells. CT technology has also contributed to the mitigation of the potential reliability issues resulting from the storage of increasing amount of data bits per cell. More information on CT technology is available at the following link: Charge Trap Flash.

The below diagram shows the impact of the NAND type and cell arrangement on the capacity of the flash memories.

eMMC Flash

The term eMMC, or embedded Multi-Media Card, refers to a storage technology that is based on NAND flash cells, integrates a controller, and provides a unified standard interface. Formerly maintained by the MMC Association (MMCA), it is now standardized by JEDEC. The standard allows for extensions, such as the eMMC Security Extension.

An eMMC flash memory consists of at least three basic components:

- MMC interface

- Flash controller

- NAND Flash

The flash controller implements several functionalities that aim at extending the life span of these memories:

Wear Leveling: As mentioned before, flash memories support a finite number of P/E cycles, and writing and erasing a block of memory contributes to wearing out the cells. In fact, if you erase and write always the same blocks, those blocks wear out more than the others. So, to avoid this issue, the flash controller of an eMMC flash uses a wear-leveling algorithm to determine which physical block to use each time data is being programmed. If you want to learn more about wear estimation, watch the following presentation: Wear Estimation for Devices with eMMC Flash Memory.

Error Correction Codes (ECC): In a NAND flash/eMMC device, it is to be expected that bits can have their values flip from 0 to 1 or vice versa due to noise or electromagnetic interference, which could result in data corruption. Error correction is a solution that is relying on an Error Correction Code (ECC) for detecting and correcting data corruption. The number of corrupted bits that can be detected and/or corrected depends on the type of NAND used in the eMMC and its controller.

Bad Blocks Management: Since the ECC allows for finding corrupted data, blocks in which corruption happens can be identified as well. Depending on the ECC and the number of bits that can be corrected, the controller can set a threshold on the number of corruptions allowed before any corrective action (besides correcting the data using the ECC) is taken. Once this limit is reached, the data is corrected and moved to another block in the device. The block in which the recurring corruption has happened can be marked as a bad block. These blocks will no longer be used for storing data.

Overprovisioning: Since bad blocks are expected to appear as a consequence of the wearing out of the cells, a solution is required for making sure that bad blocks can be marked bad, moved out of order, and their contents can be relocated to blocks that are functional. Overprovisioning is a solution aimed at achieving this goal by including extra storage capacity that is not visible to the host as available storage space. This improves the endurance of the eMMCs and may contribute to an improved writing performance as well.

Flash Memory on Toradex products

The following table summarizes the flash type, NAND type, and cell arrangement combinations of the various flash memories used in Toradex SoMs.

| Flash Capacity | Flash Type | Cell Type and Arrangement |

|---|---|---|

| 128MB | Raw NAND | SLC |

| 256MB | Raw NAND | SLC |

| 512MB | Raw NAND | SLC |

| 1GB | Raw NAND | SLC |

| 4GB | eMMC | 2D MLC |

| 8GB | eMMC | 2D MLC |

| 16GB | eMMC | 2D MLC / TLC¹ |

| 32GB | eMMC | TLC |

- ¹: Earlier HW versions feature 2D MLC eMMCs, succeeding HW versions feature 3D TLC eMMCs. Please check the revision history of your specific product configuration for identifying the HW version that has implemented the cell type and arrangement change from 2D MLC to 3D TLC.

The table below is summarizing the most important characteristics of NAND flash memories used in Toradex products.

| Flash Configuration | Endurance | Lifetime | Performance | Cost per Capacity |

|---|---|---|---|---|

| Raw NAND (SLC) | Highest | Highest | Highest | High |

| eMMC (2D MLC) | High | High | High | Medium |

| eMMC (TLC) | High | High | High/Medium | Low |

Some of the advantages of 3D TLC eMMCs:

- Higher density and higher capacity as more data bits are stored in the cells, and several layers are applied atop of each other.

- Improved reliability as the coupling between neighboring cells is reduced due to the increased space between the cells.

- Lower power consumption as the process sizes are smaller and the leakage current is reduced due to the CT technology.

A potential disadvantage of 3D TLC eMMCs is that their endurance is typically lower than that of the 2D MLC eMMCs. However, the increased capacities, the previously described mechanisms employed by the memory controller and the so-called pseudo-SLC (pSLC) mode can effectively eliminate this. For a detailed description of this topic, see the next chapter and the article: eMMC (Linux).

Tuning the endurance

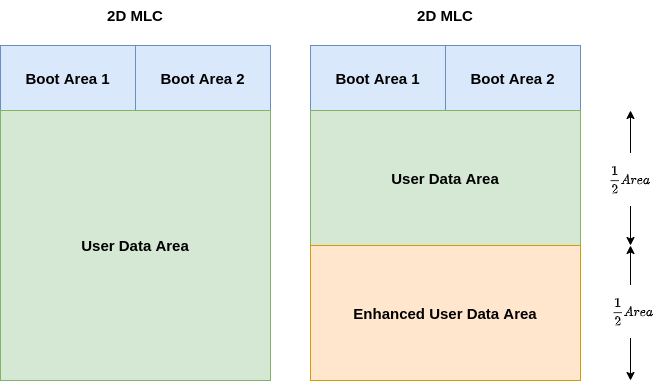

Endurance is a challenge when it comes to eMMCs based on NAND flash technology. In order to improve the endurance, reliability, and performance of the eMMCs, the hardware area partitions of the eMMC can be configured to use different modes. The so-called Enhanced User Data Area (EUDA) mode is standardized by JEDEC and supported by eMMCs implementing the JEDEC eMMC standard 4.4 or higher. In enhanced mode, cells are set to pseudo-SLC (pSLC) mode.

pSLC mode improves endurance and write speed significantly. For example, a 3D TLC eMMC memory that supports 3k P/E cycles in normal mode can support up to between 20k and 30k P/E cycles when using pSLC, almost the same as a 2D MLC eMMC. In pSLC mode, the memory cells are configured to store a single data bit only (instead of 2 bits in case of MLC eMMCs and 3 bits in case of TLC eMMCs). Because of this, the available total capacity is reduced accordingly: a hardware area partition of an MLC eMMC configured to pSLC mode will have half of its original capacity (e.g. 4GB instead of 8GB), a hardware area partition of a TLC eMMC configured to pSLC mode will have a third of its original capacity (e.g. approx. 5GB instead of 16GB).

The below figure provides some hardware area partition configuration examples, one of them employing an Enhanced User Data Area partition (using pSLC mode).

Enhanced User Area and Pseudo SLC

Enhanced User Area, also referred to as enhanced storage is a mode defined in the eMMC 4.4 (MMCA 4.4) standard onwards in which the user area of the eMMC can be configured, which is meant to make that area more reliable and present better performance. How manufacturers do implement the Enhanced User Area is not defined in the standard, though. If the device supports this configuration, then the boot and RPMB area partitions must be configured as enhanced storage by default.

As of the beginning of 2019, almost all eMMCs in production support Enhanced User Area, thus they have boot and RPMB partitions with this configuration enabled by default.

Pseudo SLC, also known as pSLC, is a configuration of the MLC NAND flash memory that uses half of the cells capacity - that is, instead of 2 bits per cell, uses 1 bit per cell - to improve the reliability, performance and endurance of the eMMC. In practice, the pSLC mode is in-between SLC and MLC.

A few remarks about enhanced mode are presented below:

- Enhanced storage is a concept, whereas pSLC is an implementation.

- pSLC is a means to implement enhanced storage.

- Sometimes the terms pSLC and enhanced storage are used interchangeably, but unless explicitly stated by the eMMC manufacturer, there is no way of knowing that they really use pSLC as the underlying implementation.

- It isn't very straightforward to find information about which implementation is used for enhanced storage in the vendor datasheets.

- One can select memory regions to configure as enhanced storage. There is no need to configure the whole eMMC user area as enhanced area.

- Programming a memory region to enhanced storage is a one-time operation. That means it cannot be reverted.

- Over-provisioning of MLC is not as good as pSLC. The former does not provide any advantage in performance nor reliability, while the latter gives an endurance factor greater than 2.